OPAMP

작성일 : 2023년 08월 27일 (Sunday)

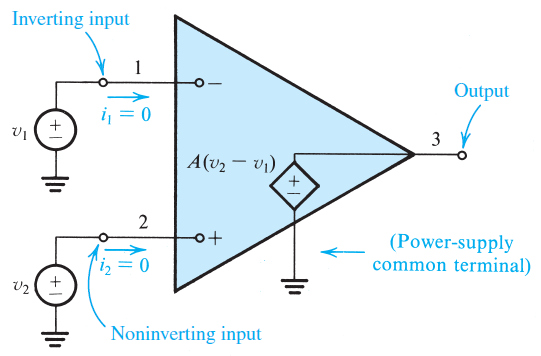

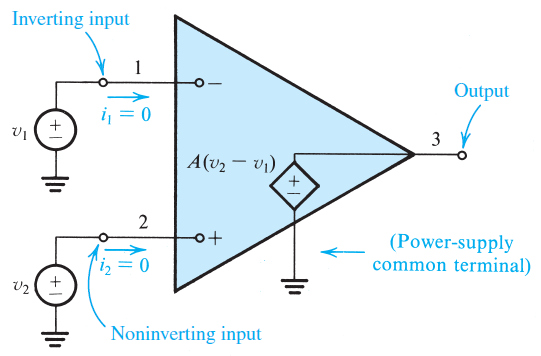

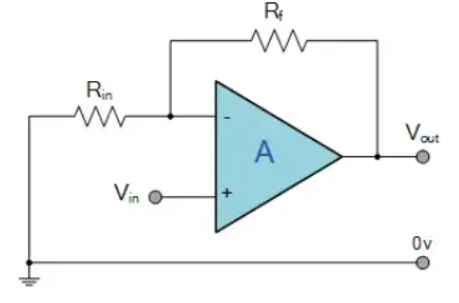

OPAMP, Operational Amplifier는 회로의 전압 신호를 증폭시킬 때 주로 사용된다. 즉, 시그널 컨디셔닝(신호를 다음 단계에서 요구하는 신호로 변환하는 일. 잡음제거, 증폭 등의 작업이 포함됨)에서 주로 사용된다고 볼 수 있다. OPAMP는 다음과 같이 표시된다.

OPAMP의 중요한 특징은 입력과 출력이 직접적으로 연결(direct-coupled)되어 있다는 것이다. 그래서 DC Amplifier라고도 한다. 이 말은 입력단과 출력단 사이에 커패시터나 변압기가 없어서 DC든 AC든 원하는 대로 증폭됨을 의미한다. OPAMP 사용시 기본적으로 주의할 점은 OPAMP의 출력단과 -입력단은 항상 피드백회로를 통해 연결되어야 한다는 것과, 증폭결과가 VCC와 VEE 이내여야 한다는 점이다.

차동이득 A (혹은 개방루프 이득)

OPAMP는 차동이득 A를 갖는다. 즉, 출력전압 $v_{O}$은 위 그림 OPAMP 를 기준으로 보았을 때 $A(v_{2} - v{1})$이 된다.

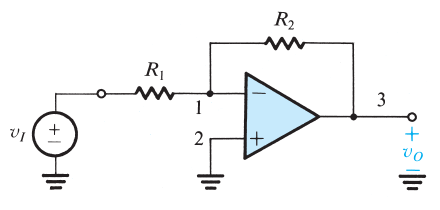

반전구성

반전구성은 반전입력쪽에만 전압을 인가하는 구성이다. 반전입력에 전압을 인가하고 아래와 같은 형태로 적절한 크기의 임피던스를 연결하면, 출력 전압을 원하는 크기로 증폭할 수 있다.

폐루프 이득 G는 $-\frac{R_{2}}{R_{1}}$이다.

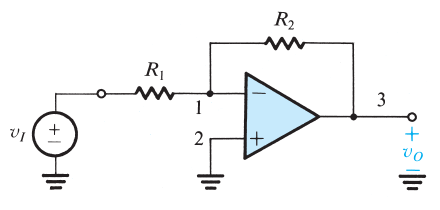

비반전구성

비반전구성은 비반전입력쪽에만 전압을 인가하는 구성이다. 비반전입력에 전압을 인가하고 아래와 같은 형태로 적절한 크기의 임피던스를 연결하면, 출력전압을 원하는 크기로 입출력을 반전시키지 않고 증폭시킬 수 있다.

폐루프 이득 G는 $1 + \frac{R_{f}}{R_{1}}$이다.

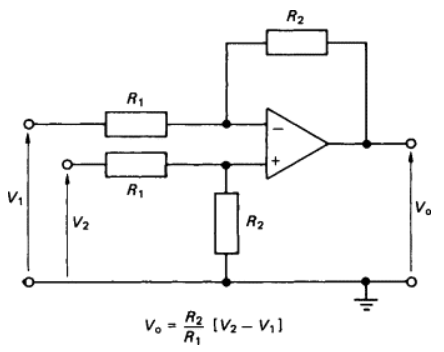

차동증폭기

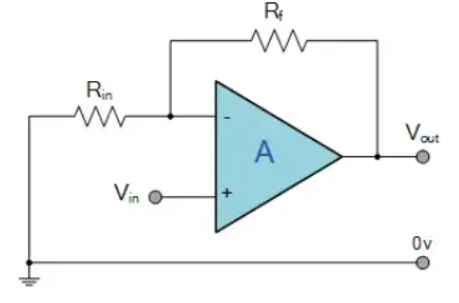

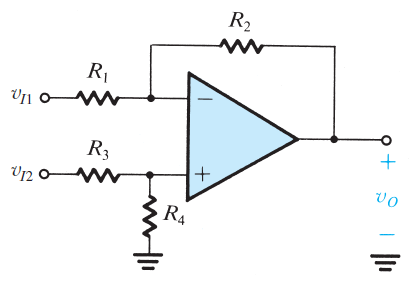

차동증폭기는 비반전입력에서 반전입력을 뺀 차동입력 값을 증폭시키기 위한 회로이다. 주로, 회로 내에서 두 지점 사이의 전압의 차를 구해 특정 소자에 걸리는 전압을 정밀하게 측정하기 위해 사용된다. 하지만, 어쩔 수 없이 비반전입력과 반전입력에 공통적으로 들어오는 동상 입력에 대해서도 증폭이 이루어진다. 차동증폭기는 차동신호를 증폭하기 위한 소자이기 때문에 차동증폭기의 성능은 공통모드 거부비율 (CMRR; Common-Mode Rejection Ratio) 로 평가된다.

$$ CMRR = 20log\frac{\left\lvert A_d \right\rvert }{\left\lvert A_{cm} \right\rvert } $$

CMRR

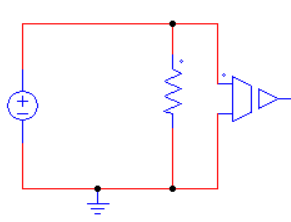

차동증폭기는 일반적으로 위와 같이 반전입력과 비반전입력의 저항의 크기를 같게하여 사용한다. 위에서 차동증폭기는 측정시 사용한다고 했는데, 예를 들어보면 아래와 같이 특정 위치의 전압을 알아야 할 때가 있는데, 비싼 전압센서를 사용하는 대신 차동증폭기와 DSP(혹은 마이컴)의 조합으로 비교적 저렴하게 센서를 대체할 수 있다.

차동증폭기는 일반적으로 계산의 편의성과 동상입력에 대한 이득을 최소화하기 위해서 비반전과 반전의 저항을 같은 값으로 설정한다. 즉, 위의 차동증폭기 그림을 참고하면, 반전 입력의 피드백 라인의 저항과 비반전 입력의 접지와 연결된 저항의 크기가 서로 같고, 분기점 (노드) 전에 있는 저항의 크기가 서로 같아야 한다는 의미이다.

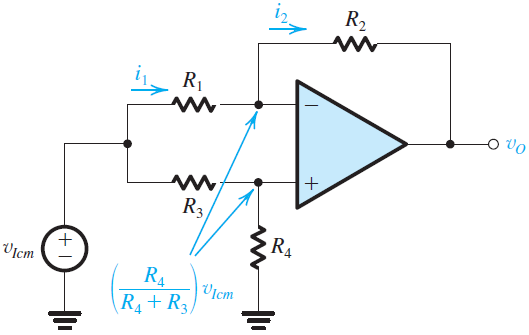

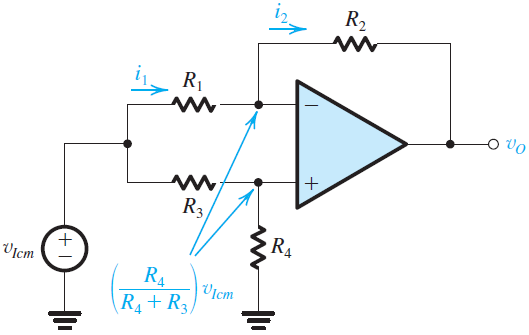

아래와 같이 비반전입력의 저항을 각각 $R_1$, $R_2$, 그리고 반전입력의 저항을 $R_3$, $R_4$로 나타냈을 때, 수식으로 차동이득과 공통모드이득을 구해보면 다음과 같다.

차동모드 이득

$$ v_{O1} = -\frac{R_2}{R_1}v_{I1} \tag{1} $$

$$ v_{O2} = v_{I2}\frac{R_4}{R_3 + R_4}(1 + \frac{R_4}{R_3}) \tag{2} $$

$$ v_{O2} = v_{I2}\frac{R_4}{R_3} \tag{3} $$

$$ v_{O} = v_{O1} + v_{O2} = \frac{R_2}{R_1}(v_{I2}-v_{I1}) = \frac{R_2}{R_1}v_{Id} \tag{4} $$

차동이득

위 (1)식과 (2)식으로 각각의 입력에 대한 반전 이득과 비반전 이득을 구할 수 있다. 그런데, (2)식을 (3)식까지 줄이고, $R_3 = R_1$, $R_4 = R_2$로 설정하면 결과적으로 $v_{O}$를 차동입력 $v_{Id} = v_{I2} - v_{I1}$에 대해서 구할 수 있게된다.

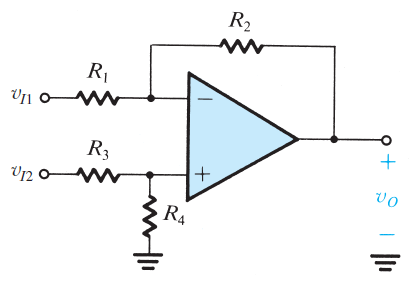

공통모드 이득

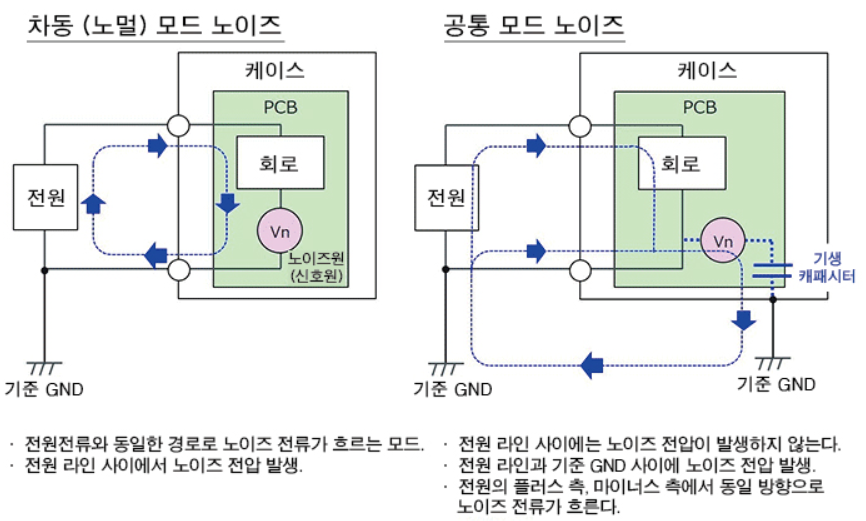

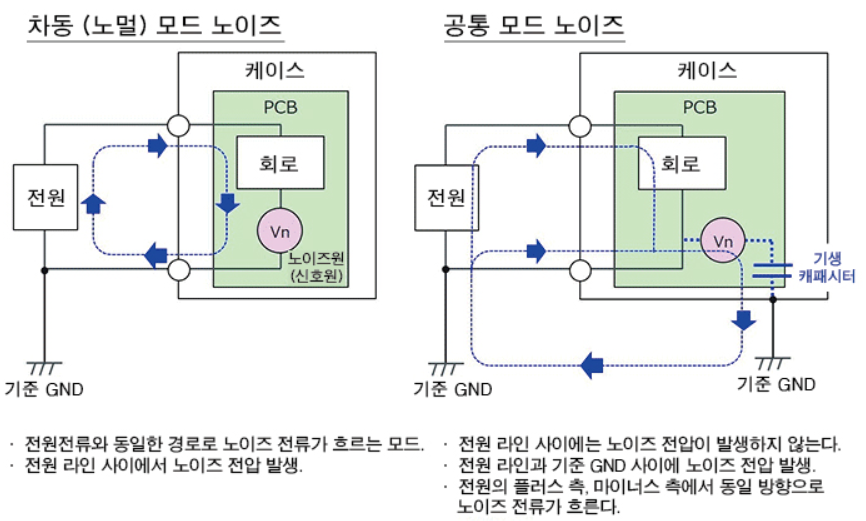

공통이득을 계산함에 앞서서, 먼저 공통모드 노이즈와 차동모드 노이즈에 대해 자세히 알아보고 넘어갈 필요가 있을 것 같다. 사실 차동모드 노이즈와 차동모드 노이즈가 어떻게 발생하는 지를 알아야 회로를 어떻게 제어할지에 대해 전략을 세울 수 있다. 차동모드는 회로에서 EMI 등에 의해서 인덕터나 커패시터에 더 많은 에너지가 들어오게 되면 순간적으로 발생할 수 있다. 그리고 공통모드는 OPAMP 등 기생 커패시터 등을 통해서 순간적으로 그라운드쪽에서 올라오는 전류인데 이 전류는 전원단의 +- 모든 방향으로 들어갈 수 있어서 공통모드 노이즈가 된다. 공통모드 노이즈를 차동증폭기를 사용하여 효과적으로 제거할 수 있기 때문에 센싱에는 보통 차동증폭기가 필수로 적용된다. 차동모드 노이즈에 의한 노이즈는 로직적으로 계산해서 대응하는 방법밖에는 없다. 이제 아래의 내용을 살펴보고 차동증폭기가 어떻게 공통모드 노이즈에 대항하는 지 알아보자.

$$ i_1 = \frac{1}{R_1}\left[ v_{Icm} - \frac{R_4}{R_3 + R_4}v_{Icm} \right] = \frac{R_3}{R_3 + R_4}\frac{1}{R_1}v_{Icm} \tag{1} $$

$$ v_o = \frac{R_4}{R3 + R4}v_{Icm} - i_2R_2 \tag{2} $$

$$ v_o = \frac{R_4}{R3 + R4}v_{Icm} - \frac{R_3}{R_3 + R_4}\frac{1}{R_1}v_{Icm} $$

$$ = \frac{R_4}{R3 + R4}(1 - \frac{R_2}{R_1}\frac{R_3}{R_4})v_{Icm} \tag{3} $$

$$ \therefore A_{cm} \equiv \frac{v_o}{v_{Icm}} = (\frac{R_4}{R3 + R4})(1 - \frac{R_2}{R_1}\frac{R_3}{R_4}) $$

공통이득

위 식에서 $i_1$은 브랜치의 전압을 각 노드의 전압차로 구할 수 있었고, 입력임피던스는 매우 크므로 $i_2$는 $i_1$과 거의 동일하다고 볼 수 있다. 따라서, 식 (2)에 식(1)을 대입하면 식 (3)이 얻어지고 여기서 우리는 공통모드 이득을 구할 수 있었다. 이 때, $R_3 = R_1$, $R_4 = R_2$ 조건을 위 (4)식에 식에 대입해보면, 공통모드 이득이 0이 된다. 하지만, 실제로 입력임피던스가 무한대가 되서 $i_1$과 $i_2$가 100% 동일해질 수는 없으므로 CMRR이 무한대인 OPAMP는 존재하지 않는다. 따라서, 공통모드 노이즈가 발생할 우려가 높다면 CMRR이 좋은 OPAMP를 사용하는 것이 좋은 선택이라고 볼 수 있겠다.

적분기

비반전 증폭기에서 $R_2$를 커패시터로 대체하면 아래와 같이 계산하여 적분기를 구할 수 있다. 아래의 식에서 $V_C$는 커패시터에 충전되어 있는 초충전압을 의미한다. 적분기, 미분기, 필터에서는 계산 상의 편의를 위해 라플라스 변환을 사용한다.

$$ \frac{V_o}{V_i} = -\frac{1}{sCR} $$

$$ v_{o}(t) = -\frac{1}{CR}\int_{0}^{t} v_{i}(t) dt - V_{C} $$

적분기

하지만, 단순히 위와 같이 회로를 구성하면 DC (w = 0 rad/s)에서는 이득이 무한대가 되기 때문에, 아주 조금의 DC만 발생해도 출력은 OPAMP의 동작전압 레벨인 L+(VCC), L-(VEE)로 조정될 수 있다는 것이다. 이득을 제한하기 위해서 음성 피드백 라인에 매우 큰 저항($R_F$)을 병렬로 달아주곤 한다. 그렇게 되면 식은 아래와 같이 조정된다.

$$ \frac{V_o}{V_i} = -\frac{R_F/R}{1 + sCR_F} $$

밀러 적분기

미분기

미분기는 적분기와 반대로 $R_2$는 저항으로 두고, $R_1$을 커패시터로 바꾸면 미분기가 된다.

$$ \frac{V_o}{V_i} = -sCR $$

$$ v_{o}(t) = -CR\frac{dv_i}{dt} $$

미분기

위에서 커패시터만 사용하여 적분기, 미분기를 고려했는데 인덕터를 사용했을 때도 수식적으로는 효과가 동일하다. 하지만, 인덕터를 계속해서 충전상태로 유지하려면 전류가 계속해서 흘러야 해서 비효율적이다. 그럼에도 사용하겠다면, 인덕터는 부피가 커서 PCB 레이아웃 상으로 탑면에 위치해야 하는데 이는 설계 상 제약이 생기기도 하고, 인덕터는 커패시터보다 더 비싸기도 하다는 점을 고려해야 할 것이다. 일반적으로는 인덕터를 OPAMP 회로에 사용하지 않는다.