FET

작성일 : 2025년 03월 23일 (Sunday)

Table of contents

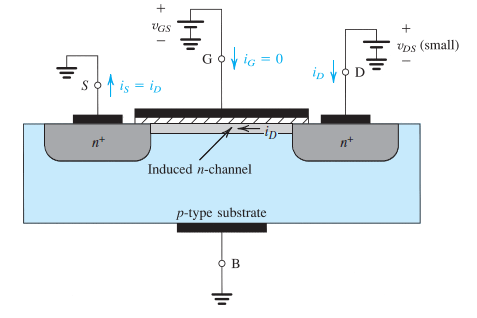

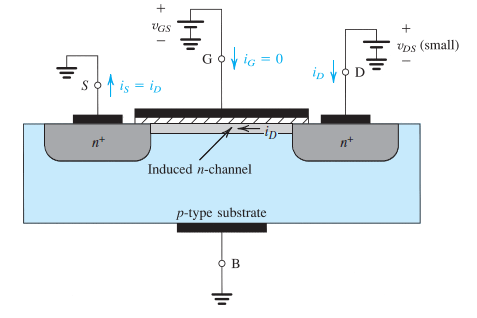

FET는 여러가지 회로에서 스위치로써 사용된다. BJT보다 누설전류가 작고, 다루기도 쉽기 때문에 널리 사용된다. FET를 간단히 설명하면 게이트, 소스, 드레인이 존재한다. 게이트에 전압을 걸어, 기판(바디)의 다수 캐리어가 밀려나면서 소스, 드레인의 다수캐리어가 이동할 수 있는 채널(통로)이 만들어진다.

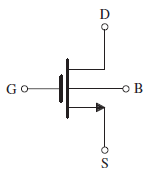

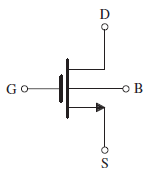

NMOS과 PMOS이 존재한다. NMOS은 전자가 소스에서 드레인쪽으로 이동하므로 전류는 드레인에서 소스 방향이다. 그리고, PMOS은 정공이 드레인에서 소스로 이동하므로 전류의 방향은 NMOS와 동일하게 드레인에서 소스 방향이다.

NMOS와 PMOS는 n-type MOSFET, p-type MOSFET 혹은 NMOS Transistor, PMOS Transistor로도 불린다. 참고로, MOSFET은 metal-oxide-semiconductor field-effect transistor의 약자이다.

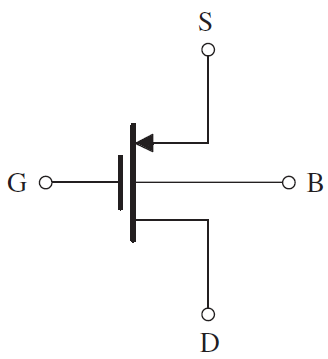

NMOS, PMOS의 회로기호는 아래와 같다.

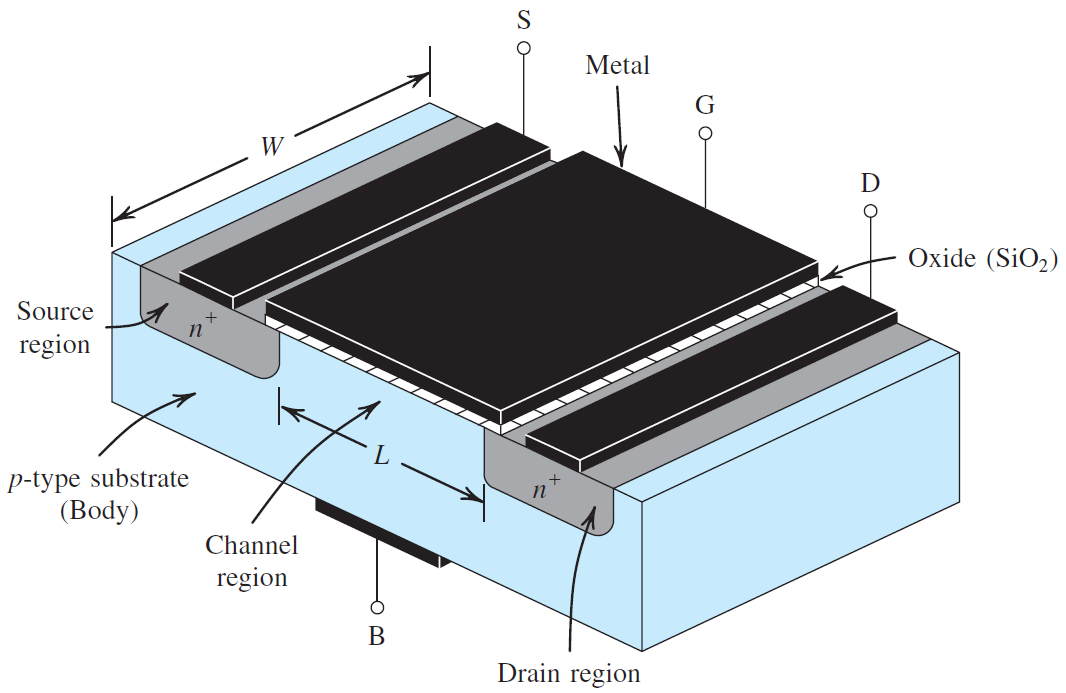

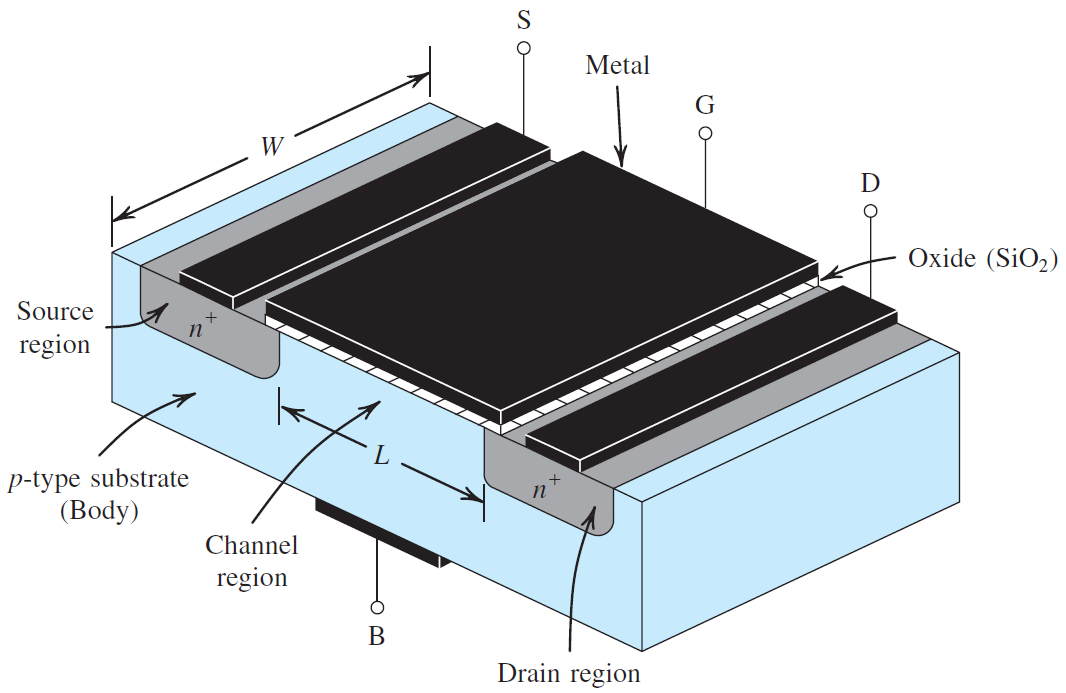

채널의 형성

채널을 형성하기 위해서는 MOSFET의 임계 전압 $V_t$를 넘어서는 게이트전압 $V_{GS}$를 인가해야 한다. $V_{GS} - V_t$가 0보다 클 때, 채널이 형상된다. $V_{GS} - V_t$는 유효전압(Effective Voltage) 혹은 초과 게이트 전압(Override Voltage)로도 불린다.

게이트 전압을 $V_{GS}$로 표기하는 이유는 게이트 전압은 소스의 전위에 대해 상대적인 값으로 인가하기 때문이다. 여기서 우리는 $V_{G}$가 아니고 $V_{GS}$라는 점을 주의깊게 보아야 할 필요가 있다. 만약, NMOS가 회로의 끝(Low Side)에서 사용되면 소스가 그라운드에 연결되니 문제가 없지만 NMOS가 회로의 중간(High Side)에서 사용된다면 키르히호프 전압 규칙에 따라서 소스의 전압은 0V 가 아니므로 $V_{GS}$는 0보다 작아질 수 있고, 이 경우 의도치 않게 모스펫이 제 때 ON이 될 수 없을 수 있다. 따라서, NMOS 위치에 따라 필수적으로 부트스트랩 회로를 사용할 필요가 있다.

채널이 형성되면, 채널에 있는 전하량 Q는 아래와 같다.

$$ \vert Q \vert = C_{OX}(WL)V_{OV} $$

채널 내 전하량

$C_{OX}$는 게이트의 금속과 P형 기판, 그리고 그 사이의 유전체 $SiO_{2}$(Silicon Dioxide; 이산화 규소)에 의해서 형성된 단위 면적당 커패시턴스이다. 그 크기는 아래와 같다.

$$ C_{OX} = \frac{\epsilon_{OX}}{t_{OX}} $$

단위 면적 당 커패시턴스

$\epsilon_{OX}$는 이산화규소의 유전율로 진공에서의 유전율의 3.9배인 $3.45 \times 10^{-11}$ F/m 에 해당한다. 그리고 $t_{OX}$는 일반적으로 4nm 수준이다. 정리하면 $C_{OX}$ 는 8.6 mF/$m^{2}$이다. MOSFET의 커패시턴스를 계산하기 위해서는 면적을 곱해야 한다. 따라서 $C = C_{OX}WL$로 표현되는데, L과 W는 $\mu$m 단위로 계산되기 때문에 편의를 위해서 $C_{OX}$를 8.6fF/$\mu m^{2}$로 표현한다. (f : femto, $10^{-15}$)

$v_{DS}$, $v_{OV}$ 크기 별 MOSFET 동작

$v_{DS}$, $v_{OV}$ 의 값의 변화에 따른 동작을 아래와 같이 나타낸다.

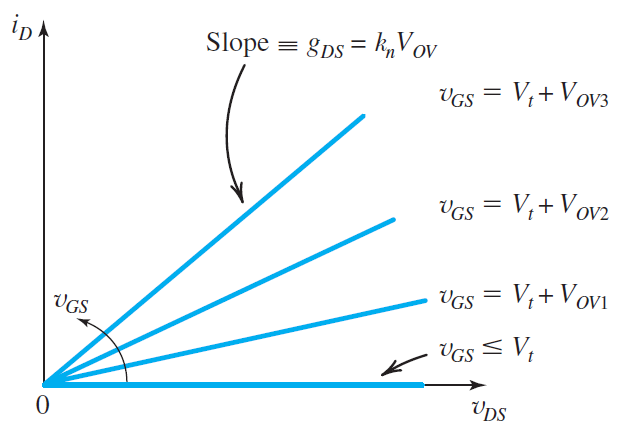

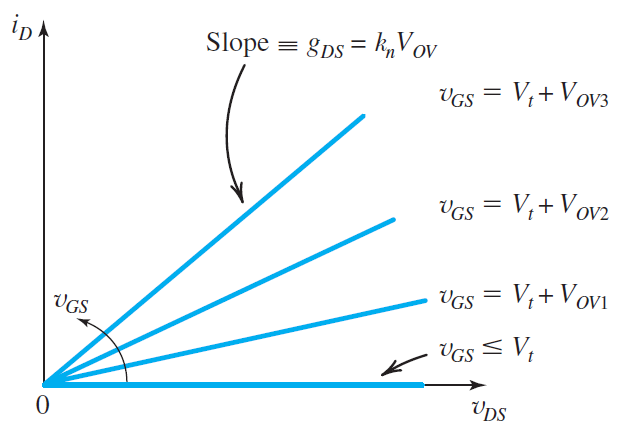

$v_{DS}$ 불변, $v_{OV}$ 가변

드레인 소스 컨덕턴스 $g_{DS}$가 $v_{OV}$에 비례하기 때문에 유효전압이 커질수록 동일 드레인-소스 전압 $v_{DS}$대비 드레인 전류가 증가한다.

$v_{DS}$ 가변, $v_{OV}$ 불변

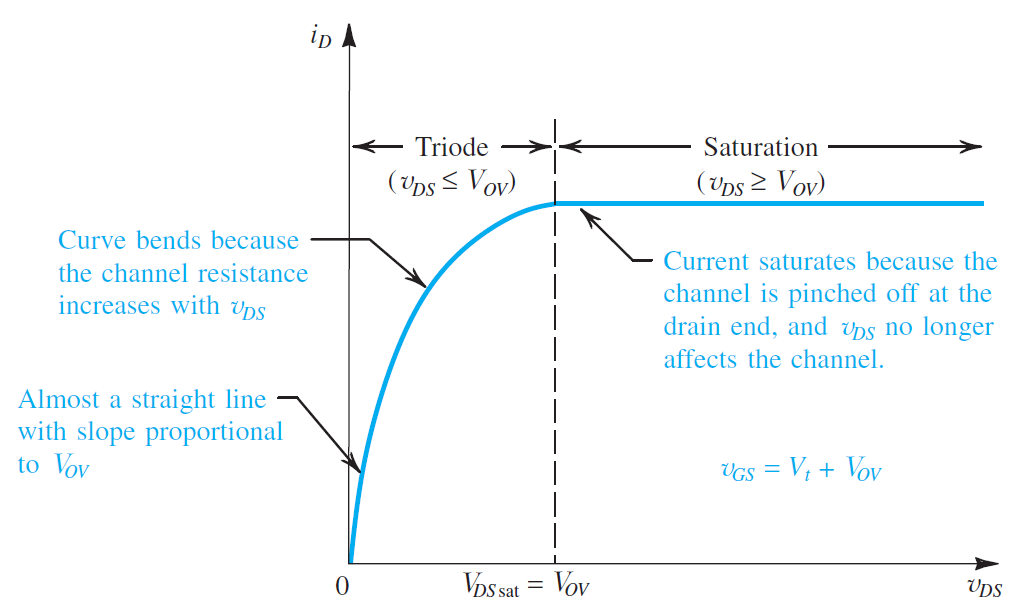

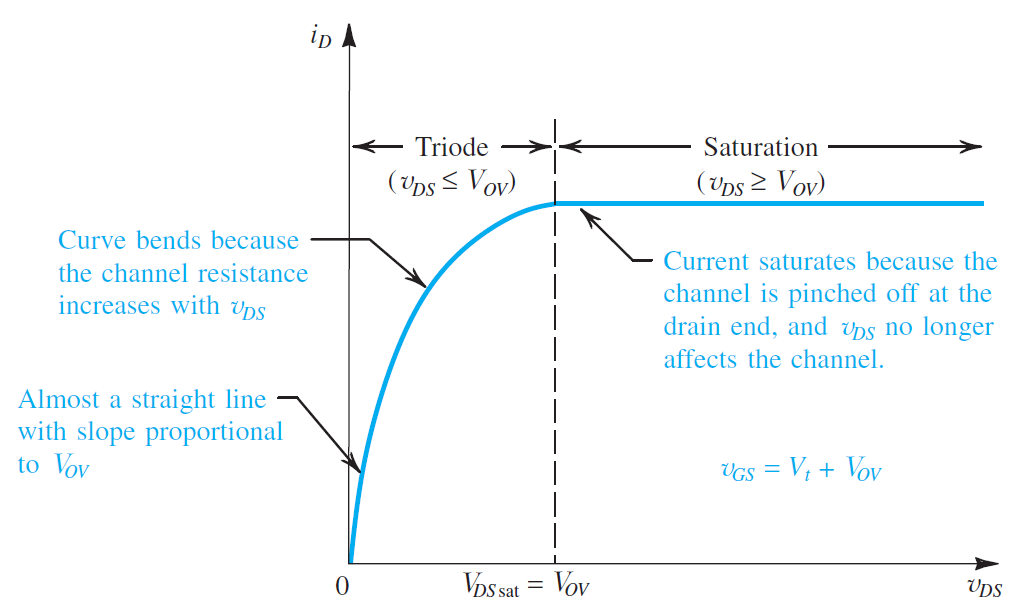

$v_{DS}$가 증가함에 따라 채널의 형태가 변형된다. 일단 $v_{DS}$ 크기에 따른 동작 모드는 아래와 같다.

위와 같이 드레인-소스 전압 별로 동작 모드가 다른 이유는 채널의 형태와 연관이 있다. $v_{DS}$를 증가시킬 수록 드레인에서의 채널의 깊이가 줄어든다. 전압의 크기가 커질수록 더 쉽게 전자가 휩쓸려가기 때문이다. 그러다가 드레인-소스 전압이 유효전압과 동일해지면, $v_{DS}$가 증가되어도 더 이상 드레인 전류가 증가하지 않는 Saturation 상태에 들어가며 채널은 핀치오프 형태가 된다. MOSFET은 일반적으로 OFF 상태와 ON (Saturation) 상태로 많이 사용된다. Triode (선형) 모드는 MOSFET을 스위치가 아닌 트랜지스터로써 사용할 수 있는 모드로 종종 사용된다.

드레인 전류 ($i_{D}$) 계산

채널이 형성되고 나면 드레인-소스 전압 $V_{GS}$에 의해서 형성된 전계에 의해 전하가 휩쓸리게 된다. 드레인 전류 식은 선형영역과 포화영역에 대해서 각각 다음과 같이 계산된다.

$$ \frac{Q}{L} = C_{OX}Wv_{OV} $$

$$ E = \frac{v_{DS}}{L} \tag{2} $$

$$ v_{Q} = \mu_{n}E = \mu_{n}\frac{v_{DS}}{L} \tag{3} $$

$$ \therefore i_{D} = \left[ (\mu_{n}C_{OX})(\frac{W}{L})v_{OV} \right] v_{DS} = \left[ k^{'}_{n}(\frac{W}{L})v_{OV} \right] v_{DS} = k_{n} v_{OV} v_{DS} $$

$$ i_{D} = g_{DS}v_{DS} $$

드레인 전류 식

전류의 정의를 떠올려보면, 단위 시간 당 전하량이므로 (1) 식의 단위 길이당 전하와 (3) 식의 전계에 의한 전자의 이동속도를 곱하면 드레인 전류가 계산된다.

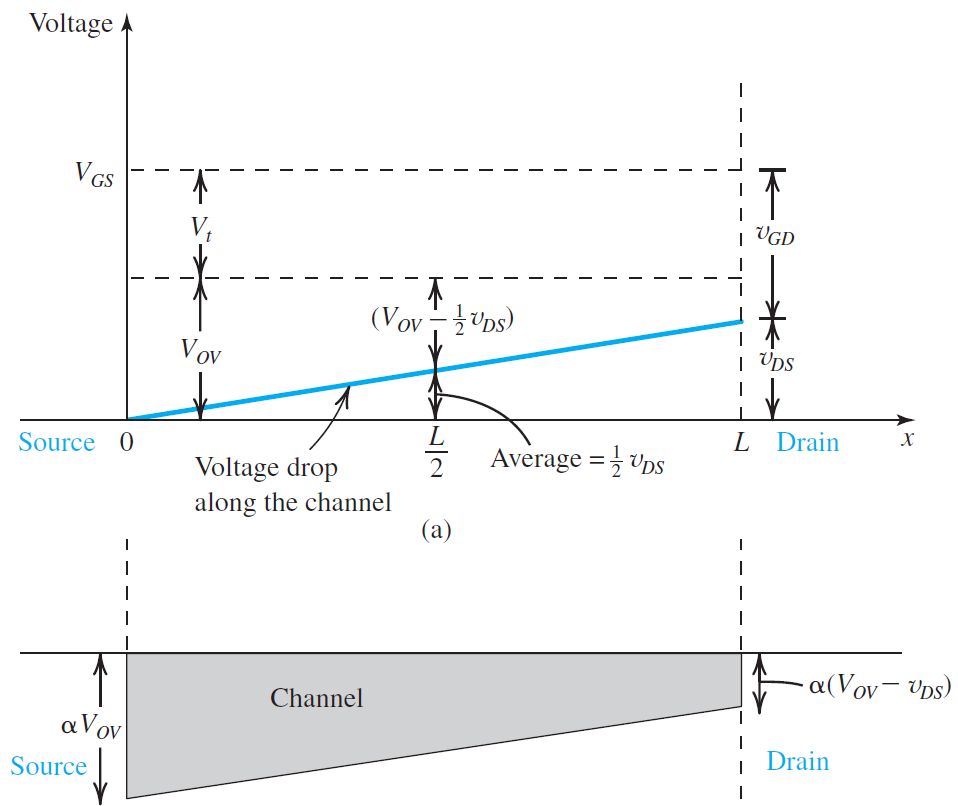

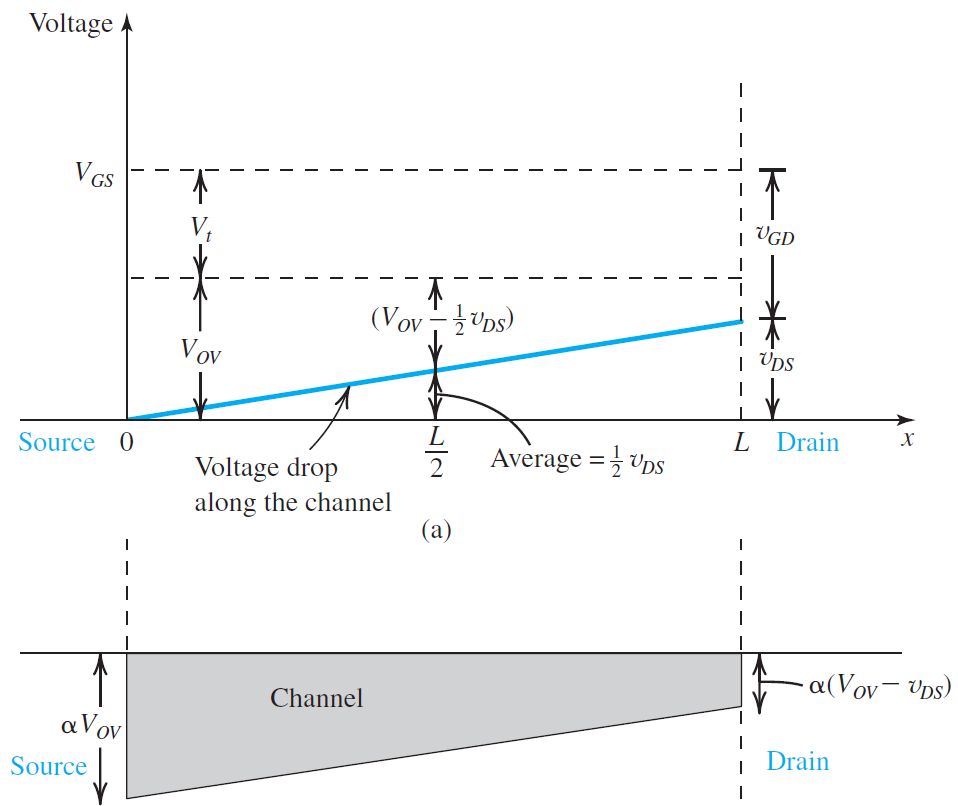

선형(Triode) 영역

$v_{DS}$가 증가하지만 선형영역에서만 동작하는 경우를 생각해보자. 채널에 전류가 흐르기 시작하면 FET의 위치에 따라서 FET가 HighSide에 위치한 경우, 소스단의 전압이 높아지므로 위의 드레인 전류식에 $v_{OV}$ 대신 $v_{OV} - \frac{v_{DS}}{2}$ 를 대입하면 식이 얻어진다. $v_{OV} - \frac{v_{DS}}{2}$은 다음의 그림에서 확인할 수 있듯이 선형 영역에서의 $v_{OV}$의 평균전압이다.

$$ i_{D} = k_{n} v_{OV} v_{DS} = k_{n} \left [ v_{OV} - \frac{v_{DS}}{2} \right ] v_{DS} $$

선형영역에서의 드레인 전류 식

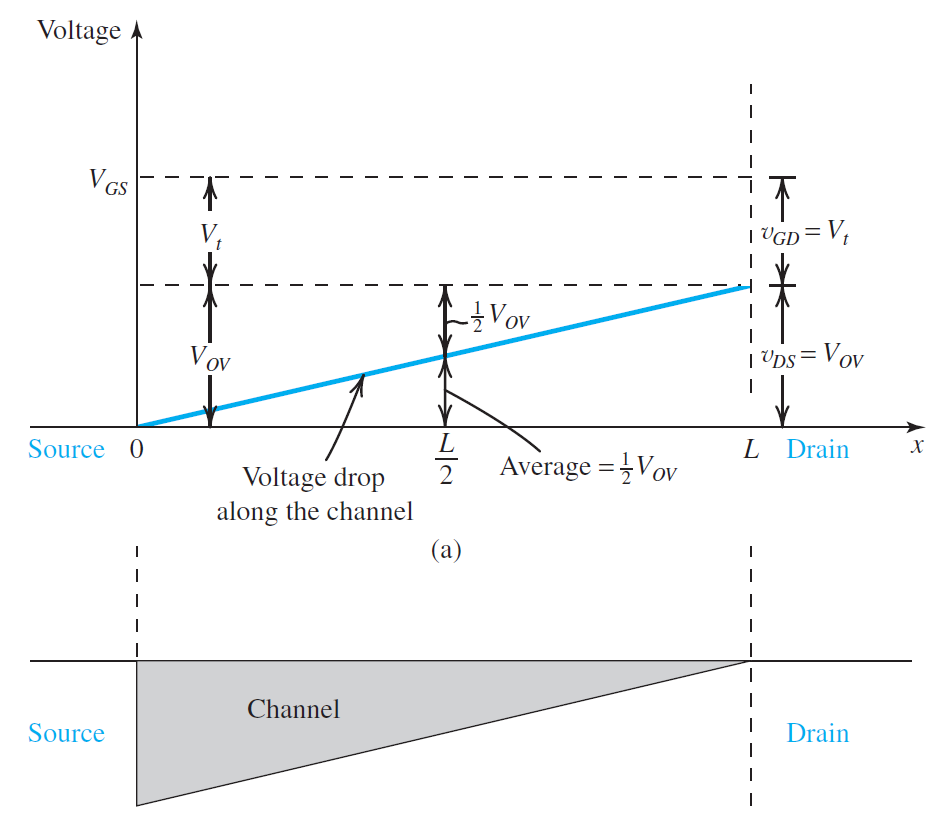

포화(Saturation) 영역

$v_{DS}$가 포화영역에서 동작하는 경우를 생각해보자. 포화영역은 $v_{DS}$가 유효전압 $v_{OV}$ 이상인 상태를 말한다. 평균값은 $\frac{v_{OV}}{2}$ 가 되므로 이를 드레인 전류식에 대입하면 식이 얻어진다.

$$ i_{D} = k_{n} v_{OV} v_{DS} = k_{n} \left [ \frac{v_{OV}}{2} \right ] v_{DS} $$

포화영역에서의 드레인 전류 식

포화영역을 진입하기 위해서는 $v_{DS}$ 가 유효전압 $v_{OV}$와 동일하면 되므로 포화영역 진입시의 드레인 전류는 다음과 같다.

$$ i_{D} = k_{n} v_{OV} v_{DS} = k_{n} \left [ \frac{v_{OV}^{2}}{2} \right ] $$

포화영역 최초 진입시의 드레인 전류 식

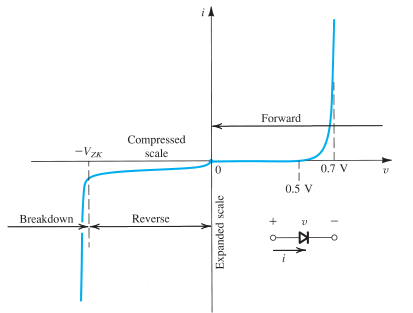

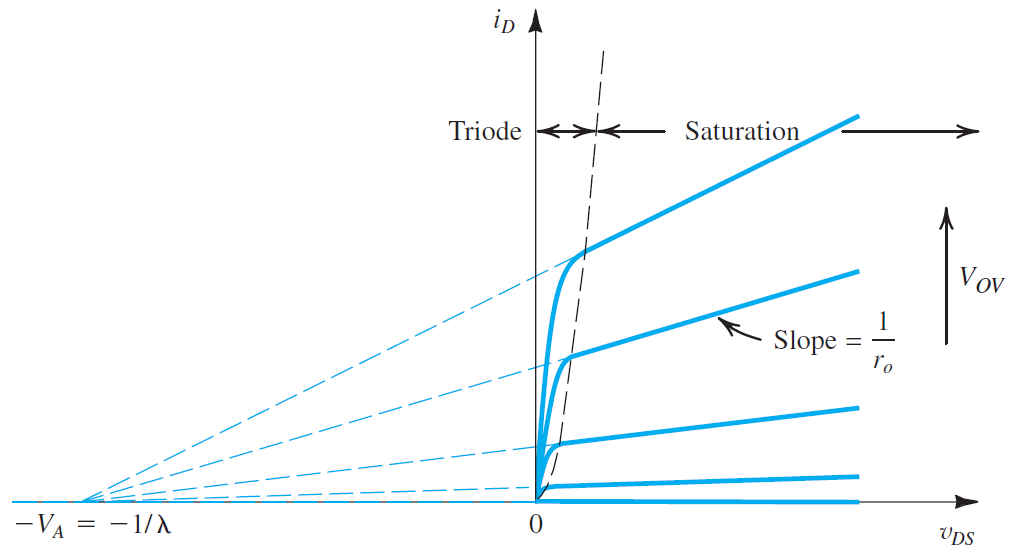

채널 길이 변조시

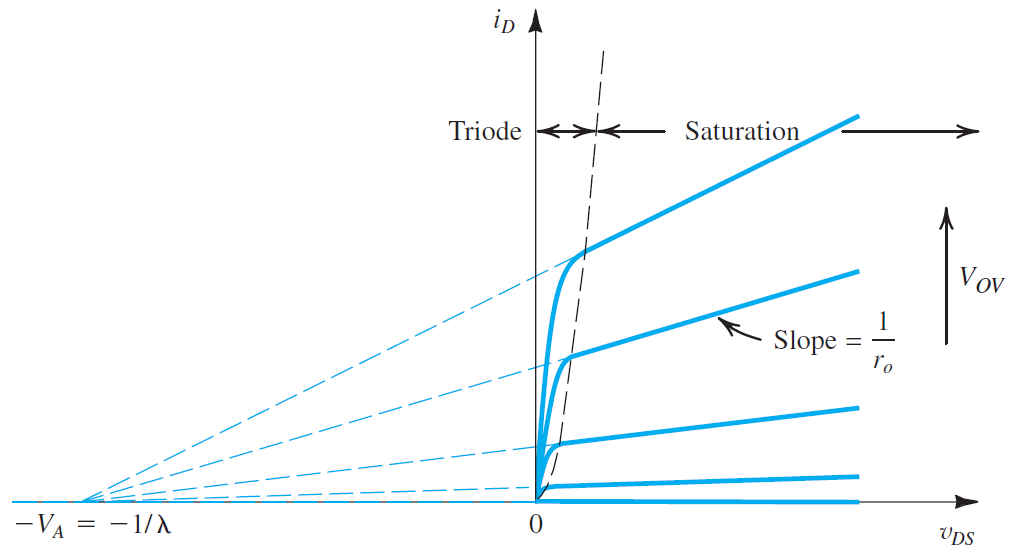

$v_{DS}$의 크기에 따라서, 삼극관 (Triode) 모드, 포화 모드로 구분된다고 했는데 그렇다면 $v_{DS}$가 유효전압을 넘어가게 되면 어떻게 될까? 위에서는 $v_{DS}$의 크기가 증가해도 드레인전류가 일정하다고 했는데, 사실 이는 채널 길이 변조 효과를 고려하지 않았을 때의 이야기다. 실제로는 채널 길이가 변조되기 때문에 그림 드레인-소스 전압, 드레인전류 곡선은 아래와 같이 변형되어야 한다.

$v_{DS}$가 커질수록 채널의 길이 L은 $\delta L$만큼 감소할 수 있다. 채널의 길이가 L에서 L - $\Delta L$로 감소하면 드레인 전류도 증가하게 되므로 위 그래프의 모습이 이해가 된다. 눈여겨볼 점은 Saturation을 쭉 이어서 음의 $v_{DS}$ 까지 연결하면 모두 $-V_{A}$ (Ealry Voltage) 지점으로 모인다는 것이다.

$V_{A}$ 는 공정단계에서 결정되는 값이고, 얼리볼티지 대신 람다로도 표현하는데, $\lambda = \frac{1}{V_{A}}$ 의 관계식을 갖는다. 최신 공정이 적용된 모스펫일수록 람다 값이 커지고 있는데 이유는 채널이 점점 작아지는 형태로 공정이 개발되고 있고 이에 따라 채널 길이 변조의 효과가 크기 때문이다. 채널 길이 변조시 드레인 전류는 포화영역 최초 진입시의 드레인 전류식을 기준으로 표현되는데, 다음과 같다.

$$ i_{D} = k_{n} \left [ \frac{v_{OV}^{2}}{2} \right ] \left ( 1 + \lambda v_{DS} \right ) $$

채널 길이 변조 효과를 반영한 드레인 전류 식

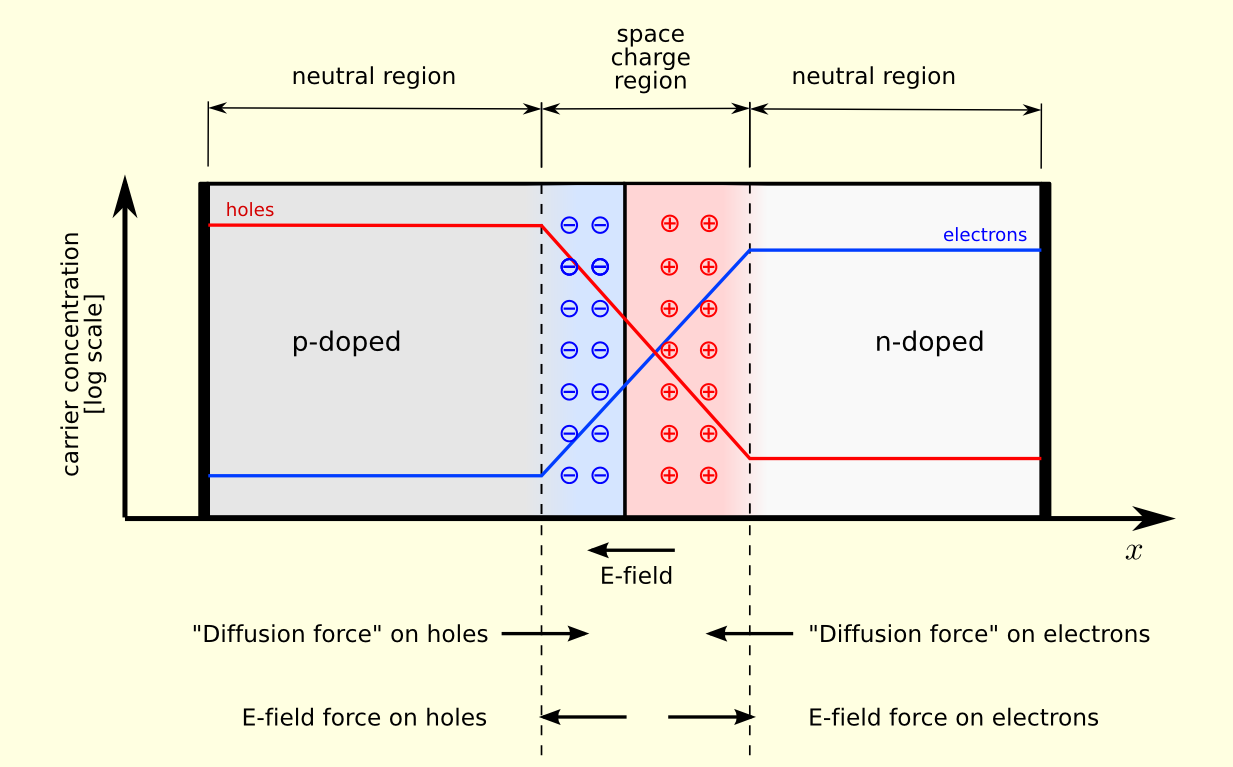

바디 다이오드

NMOS와 PMOS는 구조상 드레인-바디, 소스-바디 간 바디 다이오드가 존재한다. 따라서, ON/OFF 시 이전에 다이오드글에서 다뤘던 역방향 회복 시간이 존재하게 되므로, 필요시에는 MOSFET 데이터시트에 기재된 역방향 회복 시간 $t_{rr}$을 꼭 고려하여 회로 설계를 진행해야 한다.

MOFSET 고장 시나리오

MOSFET 역시 고장이 발생할 수 있다. 사실, 설계할 때 소자의 동작범위를 고려하여 선택하기 때문에 시스템의 동작범위 내에서는 고장이 나서는 안되지만 현실적으로 모든 물체는 시간이 지남에 따라 성능이 저하되기 때문에 피할 수 없다.

고열 발생 원인 1 : 게이트 드라이버 성능 저하(이상)

FET의 게이트 전압이 의도된 전압보다 작아지면, 채널이 작아져서 저항이 증가한다. 저항의 증가는 발열량의 증가로 이어진다.

고열 발생 원인 2 : 냉각 부족

보통 냉각을 설계할 때, FET나 다른 부품의 고장을 고려한 값으로 냉각을 하지는 않는다. 그러다보니, 주변부의 성능 저하로 인해 FET 가 쉽게 온도가 오를 수 있는 조건이 되면, 반복해서 고온에 노출되는 시간이 증가된다.

열폭주 시나리오 1 : 산사태 항복

반도체는 고온에 노출되면, 전기 에너지뿐만아니라 열 에너지로도 EHP가 발생할 수 있게 되는데, 이 EHP가 공핍영역에서의 전계를 타고 격자를 충돌시키면 산사태 항복이 일어날 확률이 높아진다.

열폭주 시나리오 2 : 유전체 유전율 저하

유전체 역시 고온에 노출되면 좋을게 없다. 노온에 노출된 유전체는 전기 쌍극자가 무작위로 흐뜨러지기 때문에 유전율이 계속해서 변하기 때문에 일반적으로 유전율이 낮아지게 된다. 유전율이 낮다는 것은 축적되는 전하량이 적어진다는 의미이고, 게이트에 축적된 양전하가 적으면 채널도 작게 형성되기 때문에 채널이 작아져 더욱 더 고온에 취약해지는 상태가 되게 된다. 재빠르게 냉각하지 않으면 양성 피드백 반응에 의해 열폭주 현상으로 소손된다.

과전압 고장 시나리오 1 : 절연체 절연파괴

과전압에 의해 절연체의 절연이 파괴되며 GS 단 쇼트가 발생하며 터져버릴 수 있다. 이 경우, FET 케이스가 터져버릴 수 있다.

모스펫의 종류

PMOS

PMOS는 다수 캐리어의 종류가 다르고, 그에 따라 바이어싱을 NMOS와 다르게 해야하지만 컨셉은 동일하다. 일반적으로 NMOS가 가격도 싸고 효율도 좋아 PMOS보다 많이 쓰이지만, 게이트 전압이 작을 때 동작해야 하고 변환없이 그대로 사용하는 것이 유리할 때 PMOS를 사용한다는 점만 기억하면 될 것 같다.

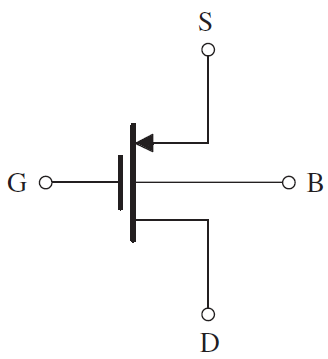

Power Mosfet (Vertical Mosfet)

Power Mosfet은 소스와 드레인이 수직으로 위치한 형태이다. 보다 넓은 채널을 갖기에 수평 모스펫보다 더 많은 드레인 전류를 가지므로 대전력에 유용하다. 일반적인 MOSFET은 고전압/대전류에서 사용할 수 없으므로 구조를 개선한 형태라고 보면 된다. 전원공급장치에서 주로 사용된다.

- 참고

- Adel S. Sedra, Kenneth C. Smith - Microelectronic Circuits